# RENESAS

# 3803 Group (Spec.H) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

# 3803 Group (Spec. H) Mask ROM version DESCRIPTION

The 3803 group (Spec. H) is the 8-bit microcomputer based on the 740 family core technology.

The 3803 group (Spec. H) is designed for household products, office automation equipment, and controlling systems that require analog signal processing, including the A-D converter and D-A converters.

# FEATURES

| ●Basic machine-language instructions             |  |

|--------------------------------------------------|--|

| Memory size                                      |  |

| ROM 16 K to 60 K bytes                           |  |

| RAM 640 to 2048 bytes                            |  |

| Programmable input/output ports                  |  |

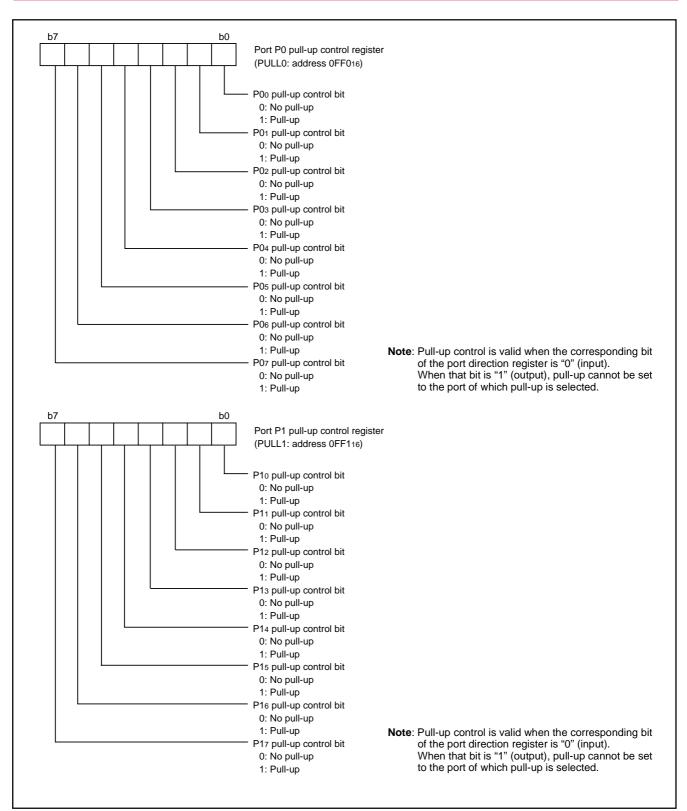

| • Software pull-up resistors Built-in            |  |

| ●Interrupts                                      |  |

| 21 sources, 16 vectors                           |  |

|                                                  |  |

| (external 8, internal 12, software 1)            |  |

| (external 8, internal 12, software 1)<br>●Timers |  |

|                                                  |  |

| •Timers 16-bit X 1                               |  |

| •Timers                                          |  |

| ●Timers                                          |  |

| ●Timers                                          |  |

| ●Timers                                          |  |

| <ul> <li>Timers</li></ul>                        |  |

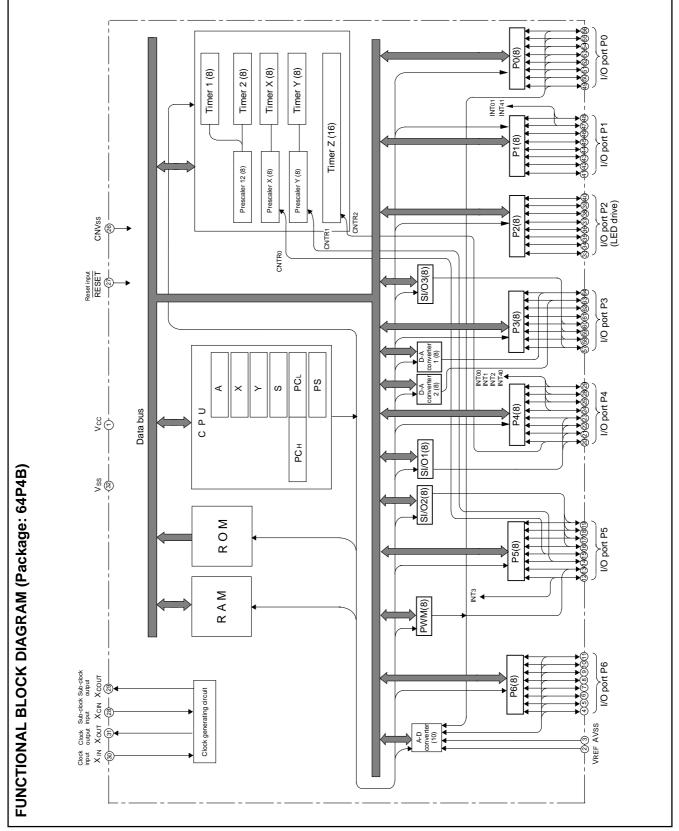

Currently support products are listed below.

## Table 1 Support products (Mask ROM version)

# REJ03B0017-0302Z Rev.3.02 Nov 05, 2004

| •D-A converter                                 |                        |

|------------------------------------------------|------------------------|

| ●LED direct drive port                         |                        |

| Clock generating circuit                       |                        |

| (connect to external ceramic resonator or quar | tz-crystal oscillator) |

| Power source voltage                           |                        |

| In high-speed mode                             |                        |

| At 16.8 MHz oscillation frequency              | 4.5 to 5.5 V           |

| At 12.5 MHz oscillation frequency              | 4.0 to 5.5 V           |

| At 8.4 MHz oscillation frequency               | 2.7 to 5.5 V           |

| At 4.2 MHz oscillation frequency               |                        |

| At 2.1 MHz oscillation frequency               |                        |

| In middle-speed mode                           |                        |

| At 16.8 MHz oscillation frequency              | 4.5 to 5.5 V           |

| At 12.5 MHz oscillation frequency              |                        |

| At 8.4 MHz oscillation frequency               |                        |

| At 6.3 MHz oscillation frequency               |                        |

| In low-speed mode                              |                        |

| At 32 kHz oscillation frequency                | 1.8 to 5.5 V           |

| Power dissipation                              |                        |

| In high-speed mode                             | 40  mM(typ)            |

| (at 16.8 MHz oscillation frequency, at 5 V po  |                        |

|                                                |                        |

| In low-speed mode                              |                        |

| (at 32 kHz oscillation frequency, at 3 V powe  |                        |

| • Operating temperature range                  | –20 to 85°C            |

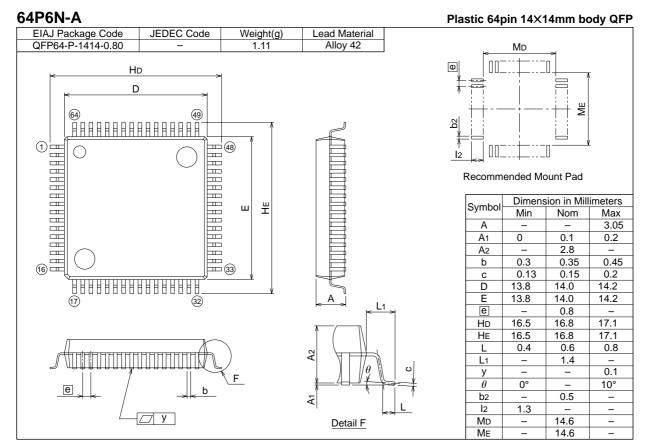

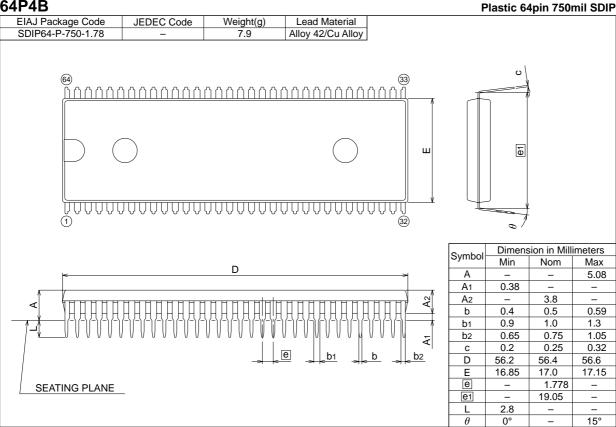

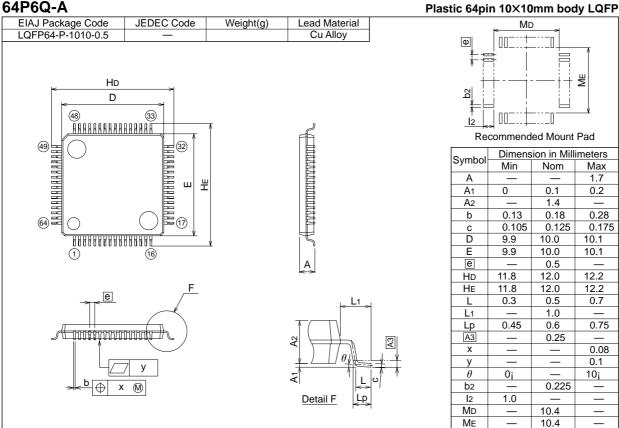

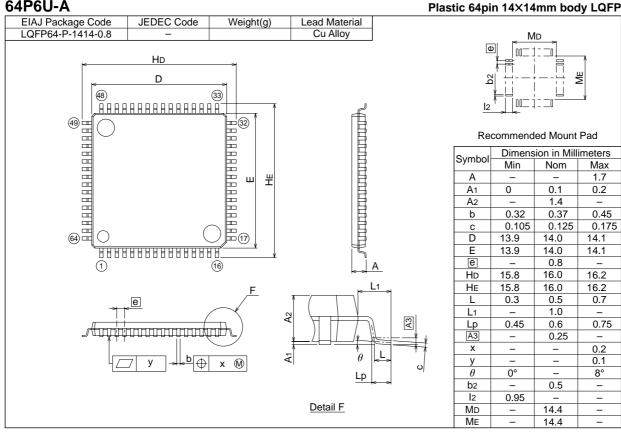

| • Packages                                     |                        |

| SP                                             |                        |

| FP 64P6N-A (64-pir                             | ,                      |

| HP 64P6Q-A (64-pin                             |                        |

| KP 64P6U-A (64-pin                             |                        |

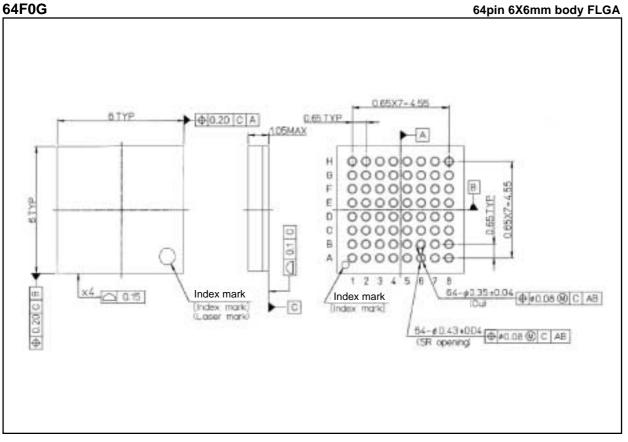

| WG64F0G (64-p                                  | oin 6 X 6 mm FLGA)     |

|                                                |                        |

| Product name    | ROM size (bytes)<br>ROM size for User in ( ) | RAM size (bytes) | Package | Remarks |

|-----------------|----------------------------------------------|------------------|---------|---------|

| M38034M4H-XXXSP |                                              |                  | 64P4B   |         |

| M38034M4H-XXXFP | 16384                                        |                  | 64P6N-A |         |

| M38034M4H-XXXHP | (16254)                                      | 640              | 64P6Q-A |         |

| M38034M4H-XXXKP |                                              |                  | 64P6U-A |         |

| M38037M6H-XXXSP |                                              |                  | 64P4B   |         |

| M38037M6H-XXXFP | 24576                                        |                  | 64P6N-A |         |

| M38037M6H-XXXHP | (24446)                                      | 1024             | 64P6Q-A |         |

| M38037M6H-XXXKP |                                              |                  | 64P6U-A |         |

| M38037M8H-XXXSP |                                              |                  | 64P4B   |         |

| M38037M8H-XXXFP | -                                            |                  | 64P6N-A |         |

| M38037M8H-XXXHP | 32768                                        | 1024             | 64P6Q-A |         |

| M38037M8H-XXXKP | (32638)                                      |                  | 64P6U-A |         |

| M38037M8H-XXXWG |                                              |                  | 64F0G   |         |

| M38039MCH-XXXSP |                                              |                  | 64P4B   |         |

| M38039MCH-XXXFP | 49152                                        |                  | 64P6N-A |         |

| M38039MCH-XXXHP | (49022)                                      | 2048             | 64P6Q-A |         |

| M38039MCH-XXXKP |                                              |                  | 64P6U-A |         |

| M38039MFH-XXXSP |                                              |                  | 64P4B   |         |

| M38039MFH-XXXFP |                                              |                  | 64P6N-A |         |

| M38039MFH-XXXHP | 61440<br>(61310)                             | 2048             | 64P6Q-A |         |

| M38039MFH-XXXKP | (01310)                                      |                  | 64P6U-A |         |

| M38039MFH-XXXWG |                                              |                  | 64F0G   |         |

Note: Electrical characteristics differ by the 3803 group standard versions and the 3803 group (spec. H). Since the 3803 group standard versions are not indicated to this data sheet, refer to "3803/3804 Group Data Sheet".

# 3803 Group (Spec. H) Flash memory version DESCRIPTION

The 3803 group (Spec. H) flash memory version is the 8-bit microcomputer based on the 740 family core technology.

The 3803 group (Spec. H) is designed for household products, office automation equipment, and controlling systems that require analog signal processing, including the A-D converter and D-A converters.

# FEATURES

| 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | tructions                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Minimum instruction execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | on time0.24 μs                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (at 16.8 MHz oscillation frequency)     |

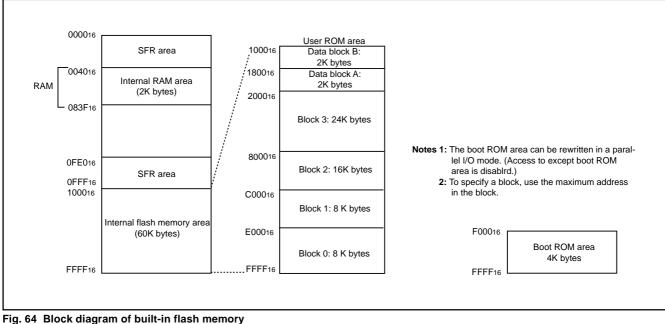

| Memory size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         |

| Flash memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60 K bytes                              |

| RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                         |

| Programmable input/output programmable programmable input/output programmable pr | ports                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Built-in                                |

| ●Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         |

| 21 sources, 16 vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (external 8, internal 12, software 1)   |

| •Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-bit X 4                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (with 8-bit prescaler)                  |

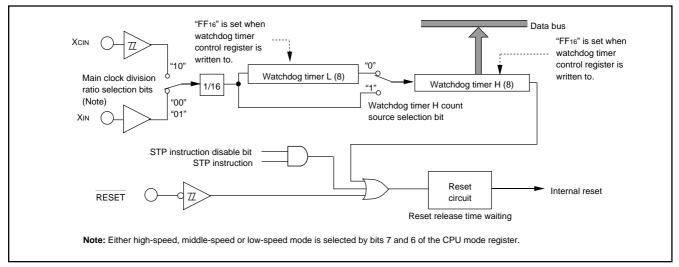

| Watchdog timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |

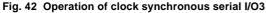

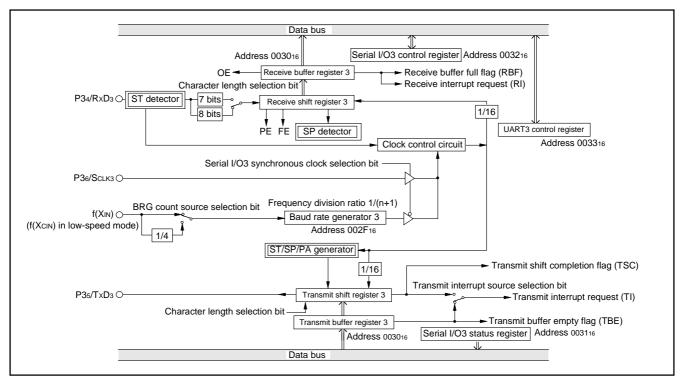

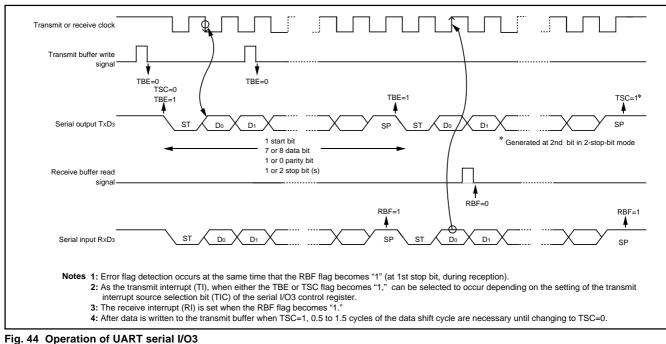

| • Serial I/O 8-bi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t X 2 (UART or Clock-synchronized)      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-bit X 1 (Clock-synchronized)          |

| • PWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10-bit X 16 channels                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (8-bit reading enabled)                 |

| •D-A converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |

| ●LED direct drive port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Built-in 2 circuits                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | resonator or quartz-crystal oscillator) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |

Currently support products are listed below.

# Table 2 Support products (Flash memory version)

| <ul> <li>Power source voltage         In high-speed mode         At 16.8 MHz oscillation frequency</li></ul> |

|--------------------------------------------------------------------------------------------------------------|

| In low-speed mode<br>At 32 kHz oscillation frequency 2.7 to 5.5 V                                            |

| <ul> <li>Power dissipation In high-speed mode</li></ul>                                                      |

| <plash memory="" mode=""><br/>Power source voltage</plash>                                                   |

•Number of times for programming/erasing ...... 100

#### ■Notes

The flash memory version cannot be used for application embedded in the MCU card.

| Product name | Flash memory size<br>(bytes) | RAM size (bytes) | Package | Remarks                              |

|--------------|------------------------------|------------------|---------|--------------------------------------|

| M38039FFHSP  |                              |                  | 64P4B   |                                      |

| M38039FFHFP  |                              |                  | 64P6N-A |                                      |

| M38039FFHHP  |                              |                  | 64P6Q-A | Vcc = 2.7 to 5.5 V Under development |

| M38039FFHKP  |                              | 0040             | 64P6U-A |                                      |

| M38039FFHWG  | 61440                        | 2048             | 64F0G   |                                      |

| M38039FFSP   |                              |                  | 64P4B   |                                      |

| M38039FFFP   |                              |                  | 64P6N-A | Vcc = 4.0 to 5.5 V                   |

| M38039FFHP   |                              |                  | 64P6Q-A |                                      |

Note: Since description, features, and electrical charactristics etc. of M38039FFSP, M38039FFFP, M38039FFHP are not indicated, refer to "3803/3804 group Data Sheet".

PRELIMINARY Notice: This is not a final specification. Some parametric limits are subject to change

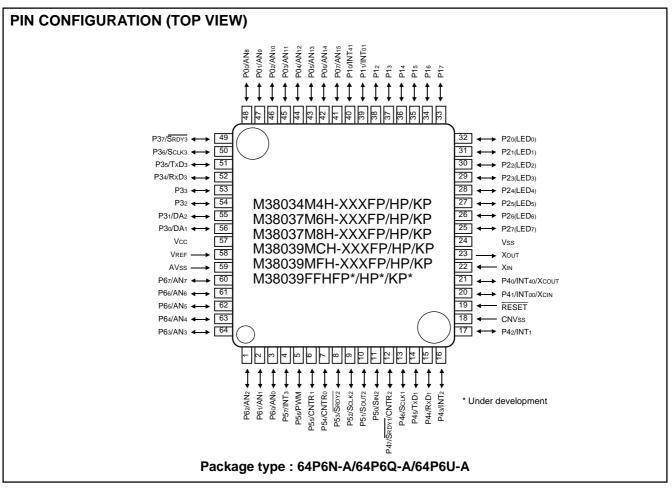

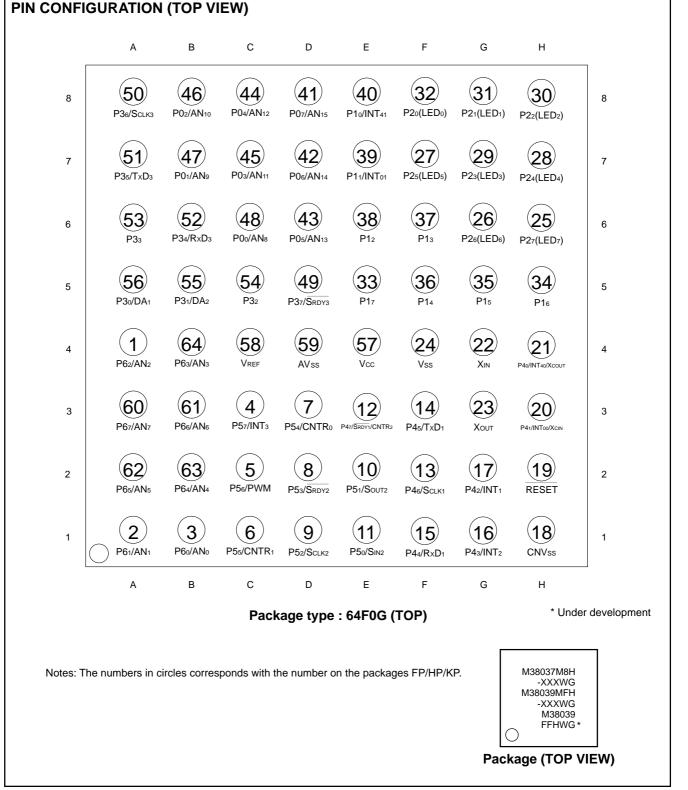

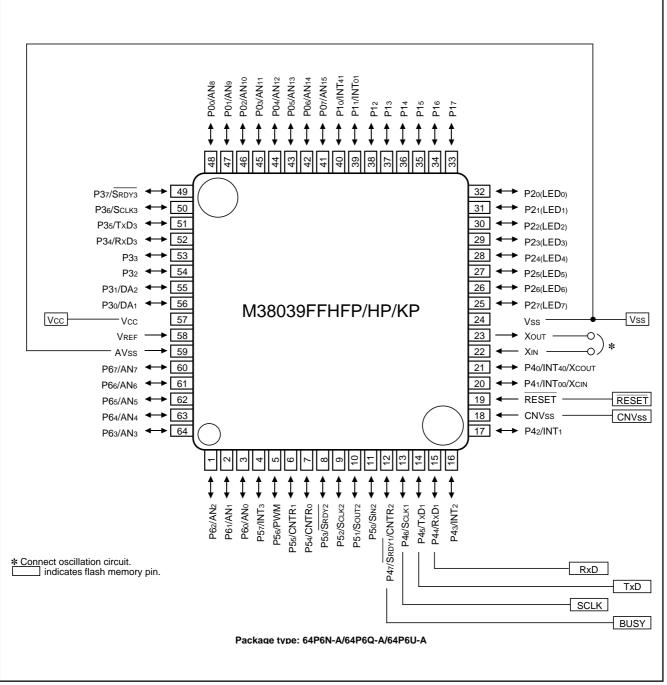

Fig. 1 3803 group (Spec. H) pin configuration

# Table 3 List of package (Spec. H)

| ble 3 List of p | ackage (Spec. H) |                                              |                  | * Under developme                     |

|-----------------|------------------|----------------------------------------------|------------------|---------------------------------------|

| Package         | Product name     | ROM size (bytes)<br>ROM size for User in ( ) | RAM size (bytes) | Remarks                               |

|                 | M38034M4H-XXXFP  | 16384 (16254)                                | 640              |                                       |

|                 | M38037M6H-XXXFP  | 24576 (24446)                                | 1024             |                                       |

|                 | M38037M8H-XXXFP  | 32768 (32638)                                | 1024             | Mask ROM version                      |

| 64P6N-A         | M38039MCH-XXXFP  | 49152 (49022)                                | 2048             | -                                     |

|                 | M38039MFH-XXXFP  | 61440 (61310)                                | 2048             | -                                     |

|                 | M38039FFHFP*     | 61440                                        | 2048             | Flash memory version                  |

| Γ               | M38039FFFP       | 61440                                        | 2048             | Flash memory version (Vcc = 4.0-5.5 V |

|                 | M38034M4H-XXXHP  | 16384 (16254)                                | 640              |                                       |

|                 | M38037M6H-XXXHP  | 24576 (24446)                                | 1024             | -                                     |

| Γ               | M38037M8H-XXXHP  | 32768 (32638)                                | 1024             | Mask ROM version                      |

| 64P6Q-A         | M38039MCH-XXXHP  | 49152 (49022)                                | 2048             | -                                     |

|                 | M38039MFH-XXXHP  | 61440 (61310)                                | 2048             | -                                     |

| Γ               | M38039FFHHP*     | 61440                                        | 2048             | Flash memory version                  |

|                 | M38039FFHP       | 61440                                        | 2048             | Flash memory version (Vcc = 4.0-5.5 V |

|                 | M38034M4H-XXXKP  | 16384 (16254)                                | 640              |                                       |

|                 | M38037M6H-XXXKP  | 24576 (24446)                                | 1024             |                                       |

| Γ               | M38037M8H-XXXKP  | 32768 (32638)                                | 1024             | Mask ROM version                      |

| 64P6U-A         | M38039MCH-XXXKP  | 49152 (49022)                                | 2048             | ]                                     |

| Γ               | M38039MFH-XXXKP  | 61440 (61310)                                | 2048             |                                       |

|                 | M38039FFHKP*     | 61440                                        | 2048             | Flash memory version                  |

Note: Since description, features, and electrical charactristics etc. of M38039FFFP and M38039FFHP are not indicated, refer to "3803/ 3804 Group Data Sheet".

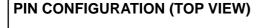

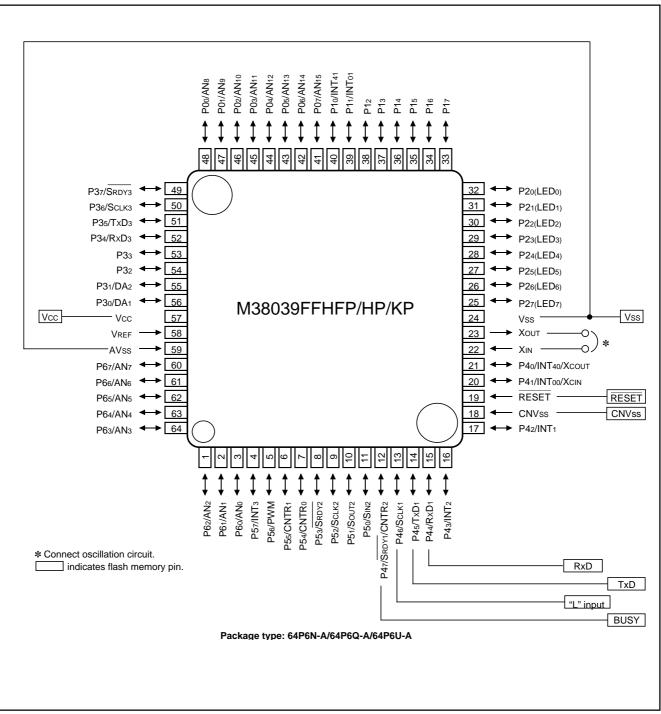

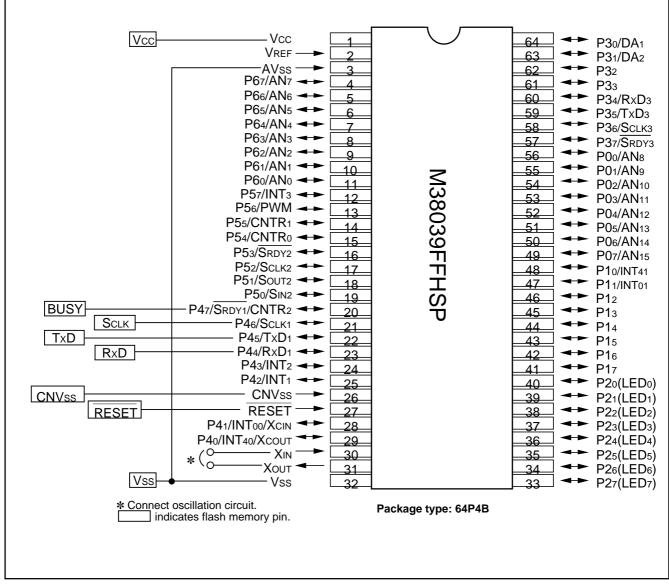

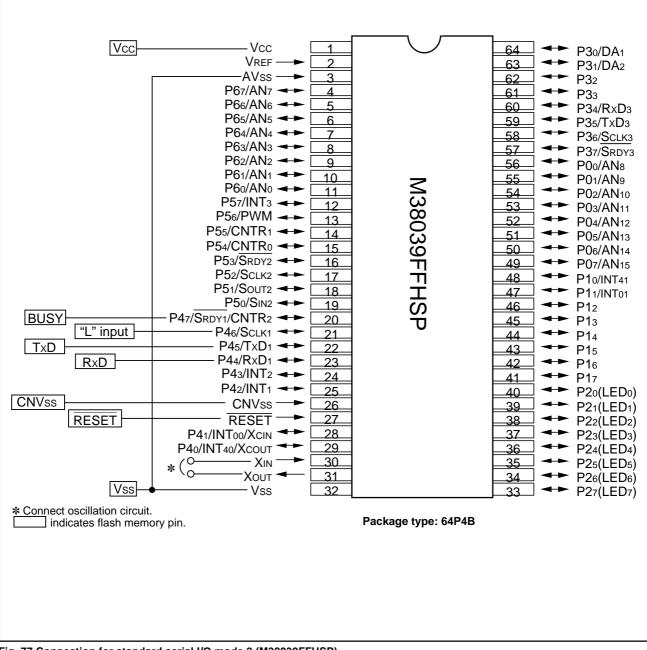

Fig. 2 3803 group (Spec. H) pin configuration

#### Table 4 List of package (Spec. H)

| Package | Product name    | ROM size (bytes)<br>ROM size for User in ( ) | RAM size (bytes) | Remarks                                |

|---------|-----------------|----------------------------------------------|------------------|----------------------------------------|

|         | M38034M4H-XXXSP | 16384 (16254)                                | 640              |                                        |

|         | M38037M6H-XXXSP | 24576 (24446)                                | 1024             |                                        |

|         | M38037M8H-XXXSP | 32768 (32638)                                | 1024             | Mask ROM version                       |

| 64P4B   | M38039MCH-XXXSP | 49152 (49022)                                | 2048             |                                        |

|         | M38039MFH-XXXSP | 61440 (61310)                                | 2048             |                                        |

|         | M38039FFHSP*    | 61440                                        | 2048             | Flash memory version                   |

|         | M38039FFSP      | 61440                                        | 2048             | Flash memory version (Vcc = 4.0–5.5 V) |

Note: Since description, features, and electrical charactristics etc. of M38039FFSP are not indicated, refer to "3803/3804 Group Data Sheet".

#### Table 5 List of package (Spec. H)

| Package  | Product name    | ROM size (bytes)         | RAM size (bytes)  | Remarks              |

|----------|-----------------|--------------------------|-------------------|----------------------|

| i ackage | 1 Todact Hame   | ROM size for User in ( ) | INAM SIZE (Dytes) | Remarks              |

|          | M38037M8H-XXXWG | 32768 (32638)            | 1024              | Mask ROM version     |

| 64F0G    | M38039MFH-XXXWG | 61440 (61310)            | 2048              | Mask ROM Version     |

|          | M38039FFHWG*    | 61440                    | 2048              | Flash memory version |

#### \* Under development

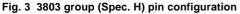

Fig. 4 Functional block diagram

# **PIN DESCRIPTION**

| Table 6 | Pin o | description |

|---------|-------|-------------|

|         |       |             |

| Pin                    | Name                | Functions                                                                                                                  | E                                               |  |

|------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|

|                        |                     |                                                                                                                            | Function except a port function                 |  |

| Vcc, Vss               | Power source        | •Apply voltage of 1.8 V – 5.5 V to Vcc, and 0 V to Vss. In the flash memory version, apply volt age of 2.7 V–5.5 V to Vcc. |                                                 |  |

| CNVss                  | CNVss input         | •This pin controls the operation mode of the chip.                                                                         |                                                 |  |

|                        |                     | Normally connected to Vss.                                                                                                 |                                                 |  |

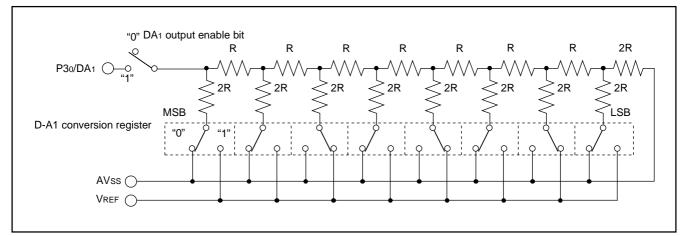

| Vref                   | Reference voltage   | •Reference voltage input pin for A-D and D-A converters.                                                                   |                                                 |  |

| AVss                   | Analog power source | •Analog power source input pin for A-D and D-A converte                                                                    | ers.                                            |  |

|                        |                     | •Connect to Vss.                                                                                                           |                                                 |  |

| RESET                  | Reset input         | •Reset input pin for active "L".                                                                                           |                                                 |  |

| Xin                    | Clock input         | •Input and output pins for the clock generating circuit.                                                                   |                                                 |  |

| Хоит                   | Clock output        | •Connect a ceramic resonator or quartz-crystal oscillator the oscillation frequency.                                       | between the XIN and XOUT pins to se             |  |

| X001                   |                     | •When an external clock is used, connect the clock sou pin open.                                                           | rce to the XIN pin and leave the XOUT           |  |

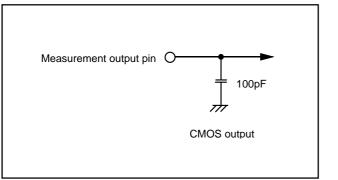

| P00/AN8-<br>P07/AN15   | I/O port P0         | •8-bit CMOS I/O port.                                                                                                      | •A-D converter input pin                        |  |

| P10/INT41              | I/O port P1         | •I/O direction register allows each pin to be individually programmed as either input or output.                           | Interrupt input pin                             |  |

| P11/INT01              |                     | •CMOS compatible input level.                                                                                              |                                                 |  |

| P12–P17                |                     | •CMOS 3-state output structure.                                                                                            |                                                 |  |

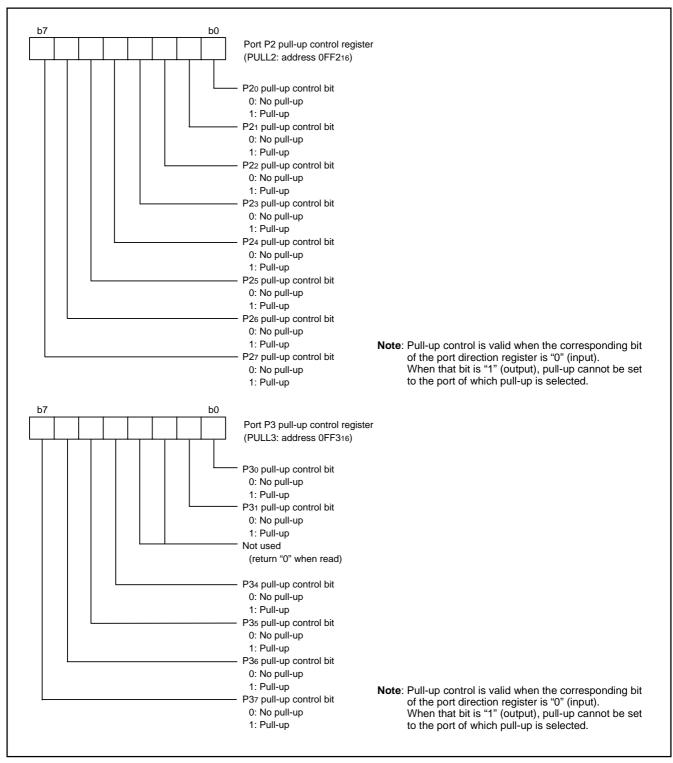

| P20-P27                | I/O port P2         | •Pull-up control is enabled in a bit unit.                                                                                 |                                                 |  |

|                        |                     | •P20–P27 are enabled to output large current for LED dri                                                                   | ve.                                             |  |

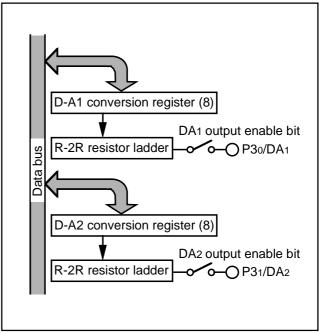

| P30/DA1                | I/O port P3         | •8-bit CMOS I/O port.                                                                                                      | •D-A converter input pin                        |  |

| P31/DA2<br>P32, P33    |                     | •I/O direction register allows each pin to be individually programmed as either input or output.                           |                                                 |  |

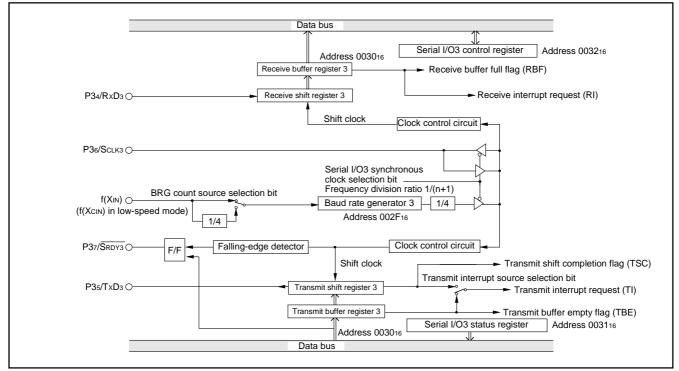

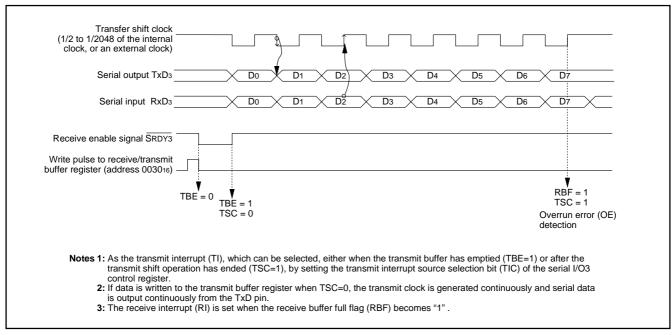

| P34/RxD3               |                     | •CMOS compatible input level.                                                                                              | •Serial I/O3 function pin                       |  |

| P35/TxD3               |                     | •P30, P31, P34–P37 are CMOS 3-state output structure.                                                                      |                                                 |  |

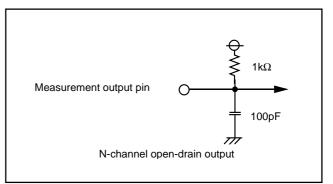

| P36/SCLK3<br>P37/SRDY3 |                     | •P32, P33 are N-channel open-drain output structure.                                                                       |                                                 |  |

| F3//3RD13              |                     | •Pull-up control of P30, P31, P34–P37 is enabled in a bit unit.                                                            |                                                 |  |

| P40/INT40/             | I/O port P4         | •8-bit CMOS I/O port.                                                                                                      | •Interrupt input pin                            |  |

| XCOUT                  |                     | •I/O direction register allows each pin to be individually                                                                 | •Sub-clock generating I/O pin                   |  |

| P41/INT00/<br>XCIN     |                     | programmed as either input or output.                                                                                      | (resonator connected)                           |  |

| P42/INT1               |                     | •CMOS compatible input level.                                                                                              | Interrupt input pin                             |  |

| P43/INT2               |                     | •CMOS 3-state output structure.                                                                                            |                                                 |  |

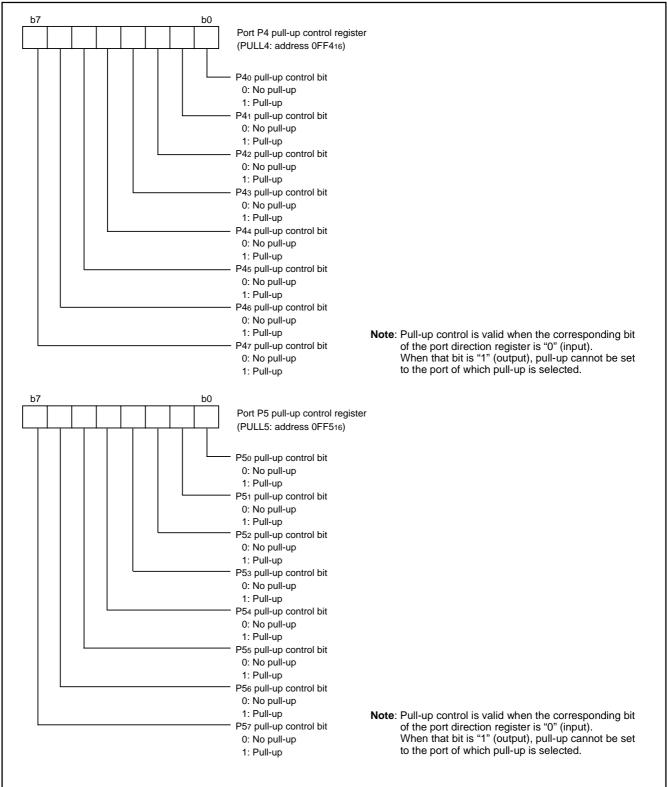

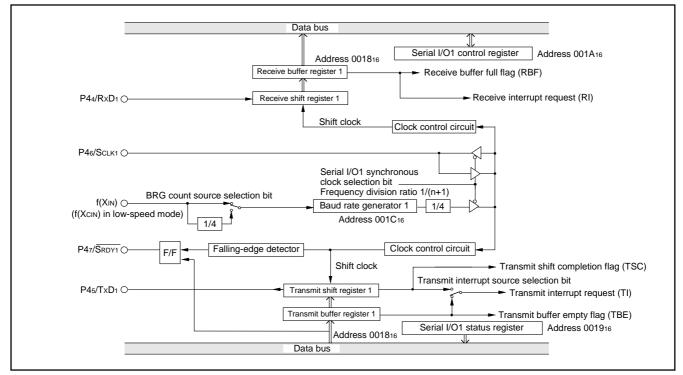

| P44/RxD1<br>P45/TxD1   |                     | •Pull-up control is enabled in a bit unit.                                                                                 | •Serial I/O1 function pin                       |  |

| P46/SCLK1              |                     |                                                                                                                            |                                                 |  |

| P47/SRDY1<br>/CNTR2    |                     |                                                                                                                            | •Serial I/O1, timer Z function pin              |  |

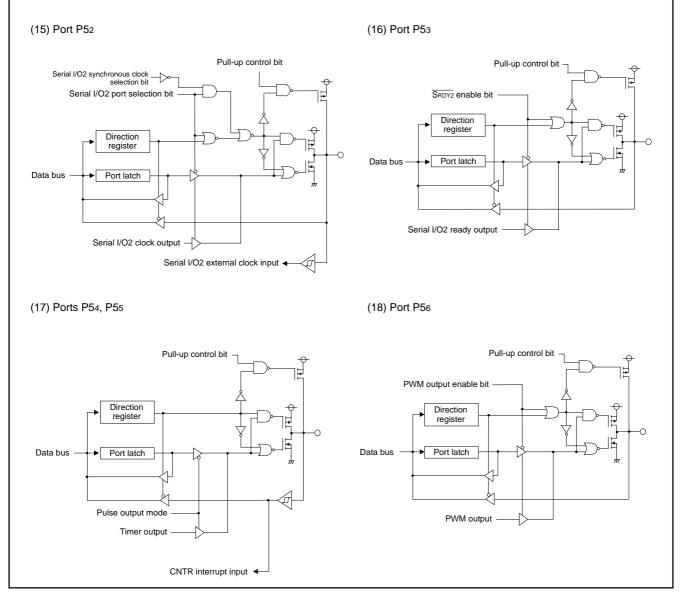

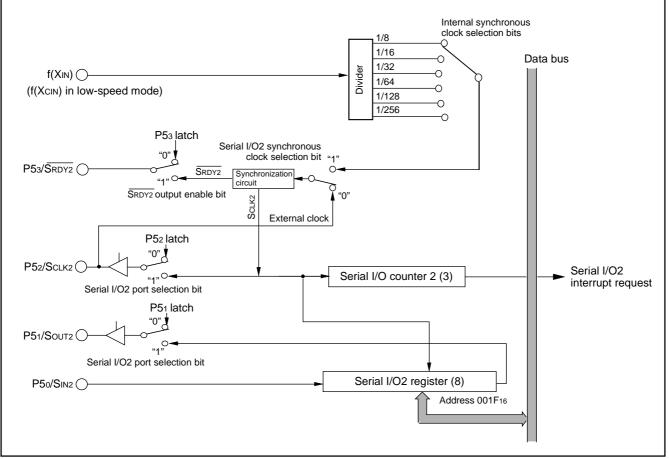

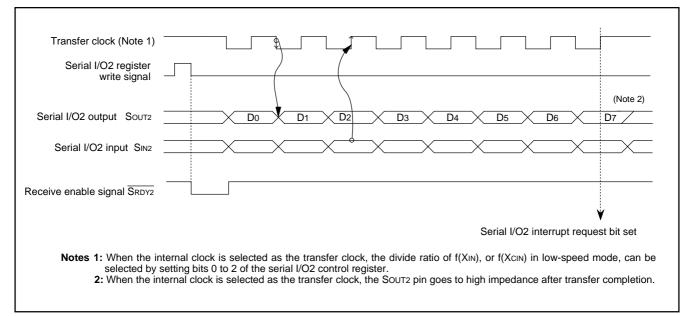

| P50/SIN2               | I/O port P5         | •8-bit CMOS I/O port.                                                                                                      | •Serial I/O2 function pin                       |  |

| P51/SOUT2<br>P52/SCLK2 |                     | •I/O direction register allows each pin to be individually programmed as either input or output.                           |                                                 |  |

| P53/SRDY2              |                     | •CMOS compatible input level.                                                                                              |                                                 |  |

| P54/CNTR0              |                     | •CMOS 3-state output structure.                                                                                            | •Timer X function pin                           |  |

| P55/CNTR1              |                     | •Pull-up control is enabled in a bit unit.                                                                                 | Timer Y function pin     PWM output pin         |  |

| P56/PWM                |                     |                                                                                                                            | •PWM output pin                                 |  |

| P57/INT3               | I/O port P6         | -                                                                                                                          | Interrupt input pin     A D converter input pin |  |

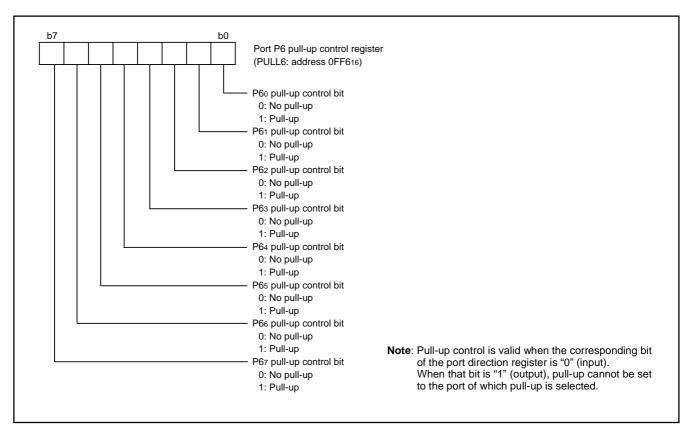

| P60/AN0-<br>P67/AN7    |                     |                                                                                                                            | •A-D converter input pin                        |  |

# PART NUMBERING

| Product name M3803 7 M 8 H – XXX SP |                                                                           |

|-------------------------------------|---------------------------------------------------------------------------|

|                                     |                                                                           |

|                                     | Package type                                                              |

|                                     | SP:64P4B                                                                  |

|                                     | FP : 64P6N-A                                                              |

|                                     | HP : 64P6Q-A                                                              |

|                                     | KP : 64P6U-A                                                              |

|                                     | WG : 64F0G                                                                |

|                                     | ROM number                                                                |

|                                     | Omitted in the flash memory version.                                      |

|                                     |                                                                           |

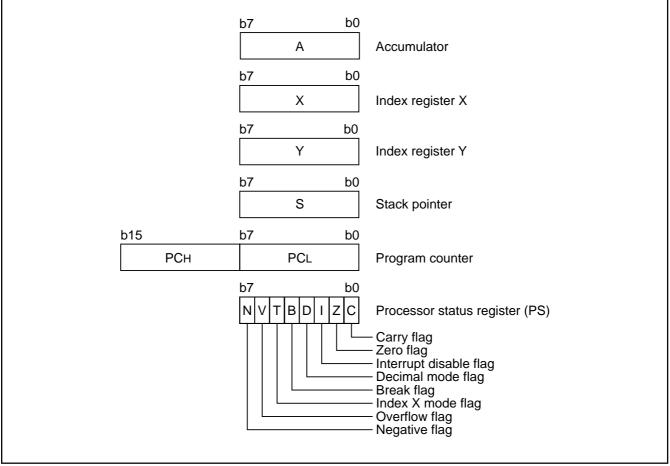

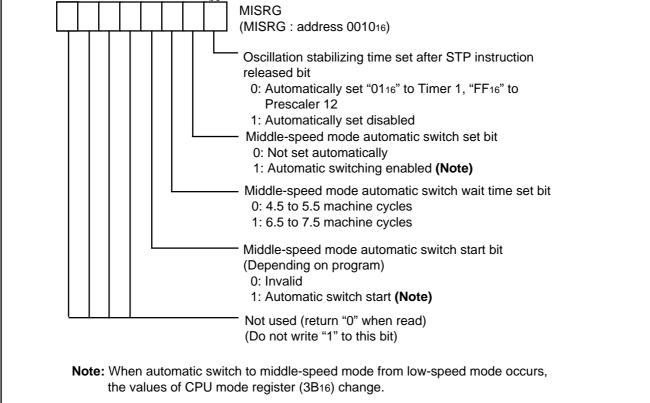

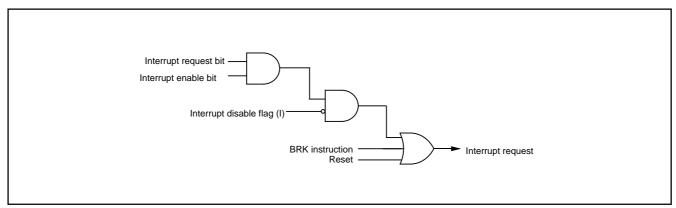

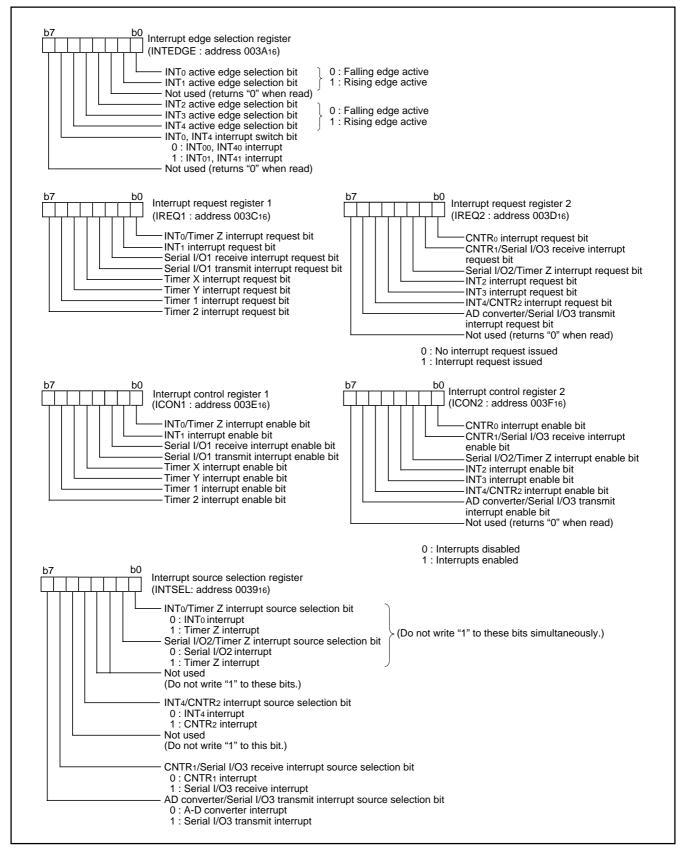

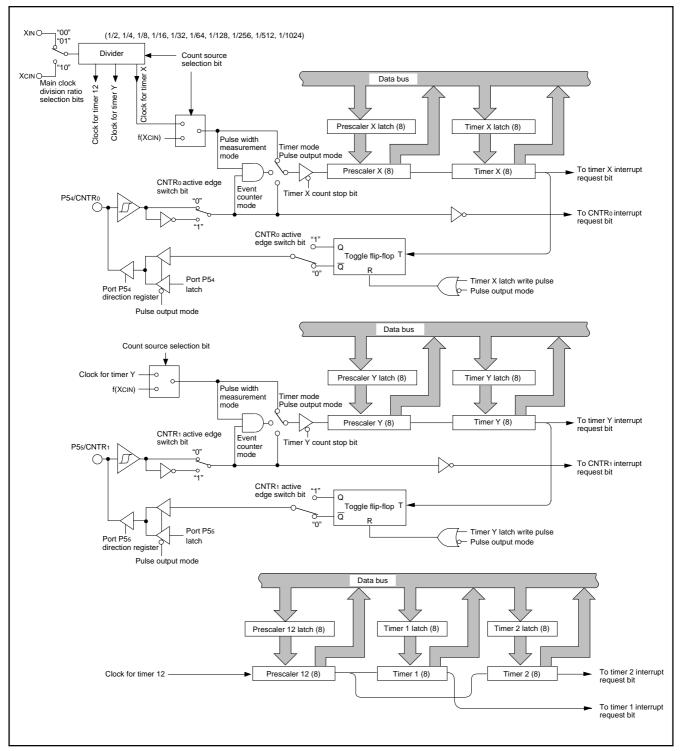

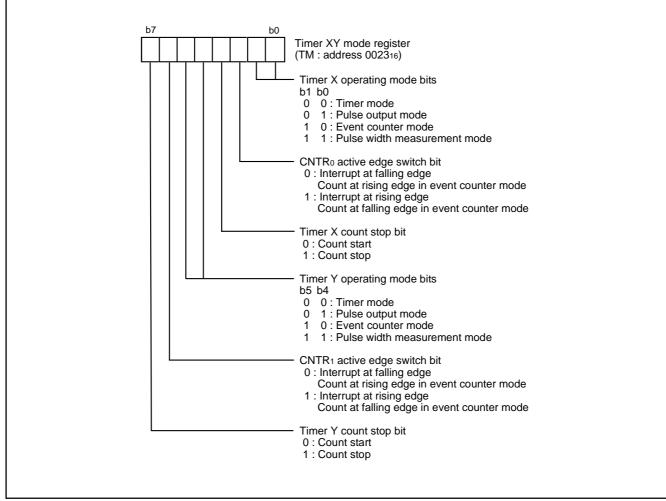

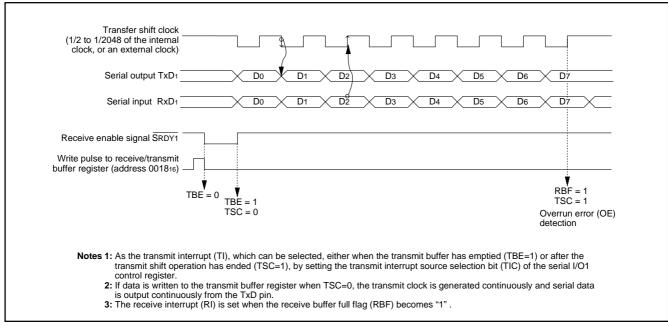

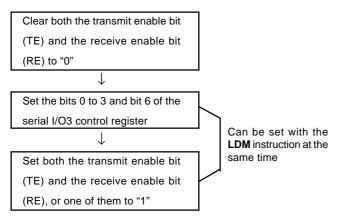

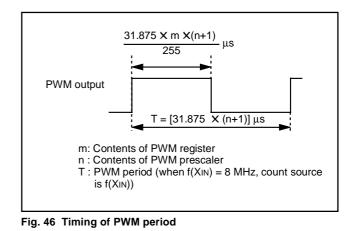

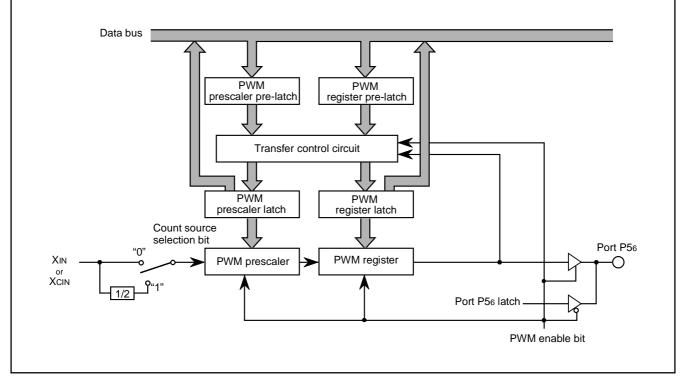

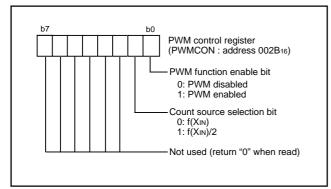

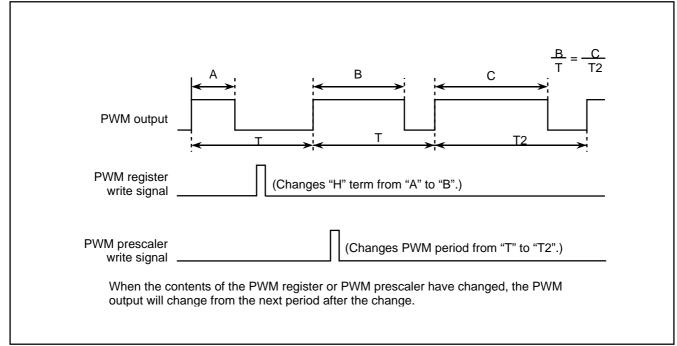

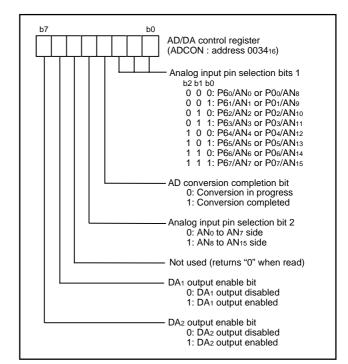

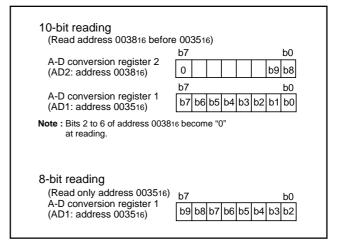

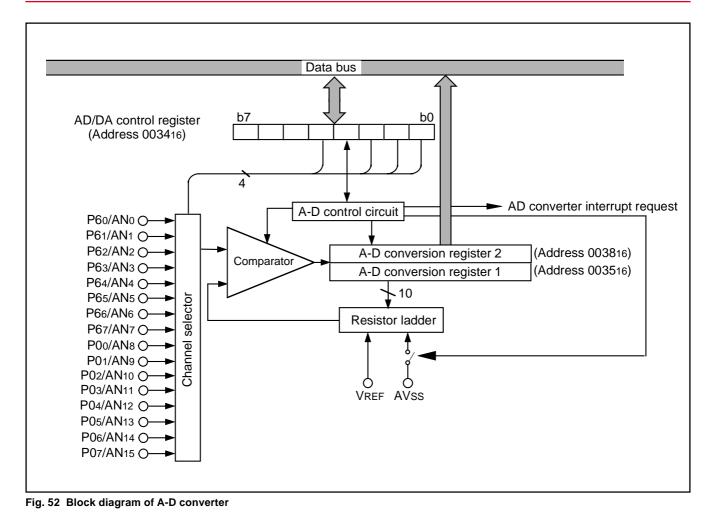

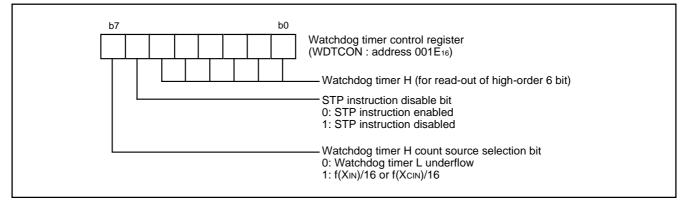

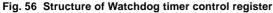

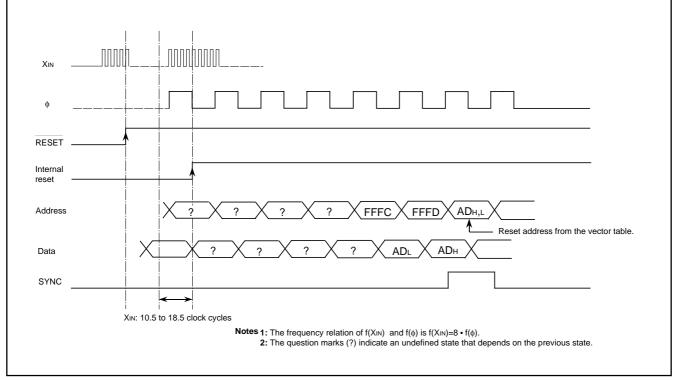

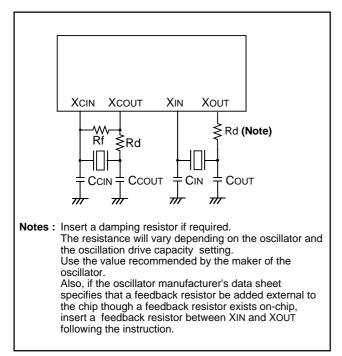

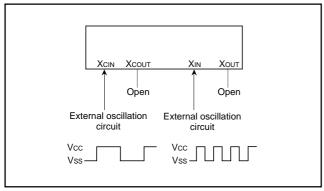

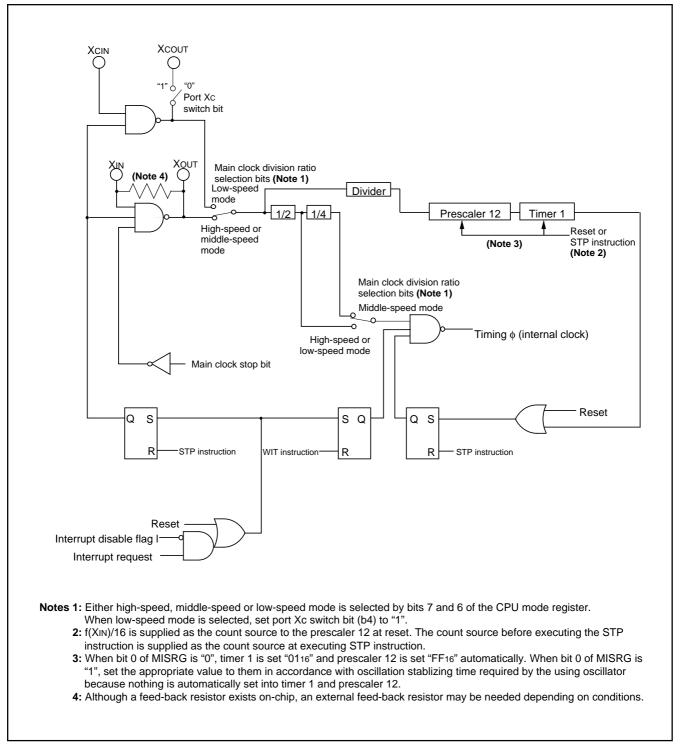

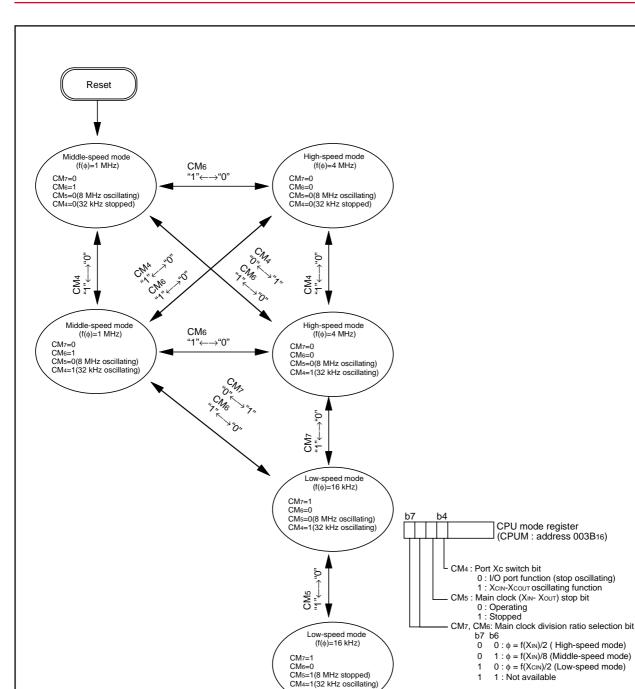

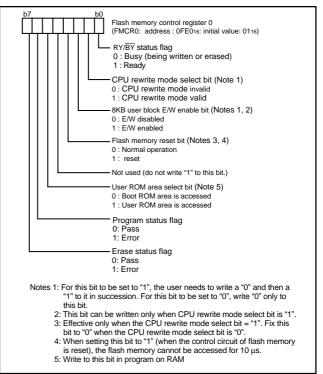

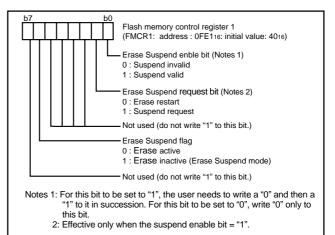

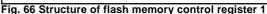

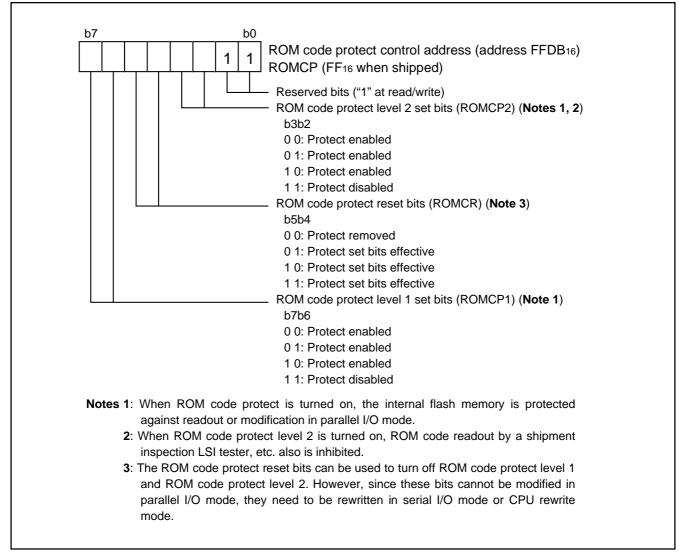

|                                     | — - : standard                                                            |