DreamSourceLab DSLogic Plus USB

L’ultimo arrivo in laboratorio è un analizzatore di stati logici della DreamSourceLab modello DSLogic Plus USB. Diamogli un’occhiata più da vicino nella dotazione hardware e nel software DSView a corredo eseguendo semplici test di segnali.

Indice - Table of Contents

Introduzione

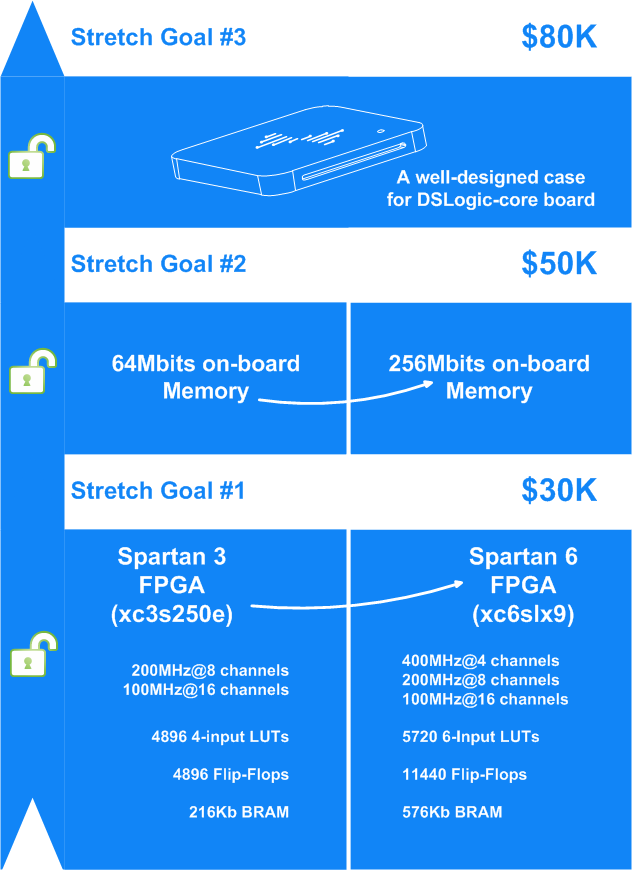

Il progetto è stato originariamente lanciato sulla piattaforma kickstarter da tre persone residenti in Cina. La raccolta fondi è andata più che bene con oltre $100.000 raccolti che ha permesso loro di seguire l’aggiornamento del prodotto in base al seguente schema riassuntivo (immagine in baso); come si vede dai lucchetti sbloccati al lato della fotografia, i passi sono stati tutti rispettati e tra breve andremo a verificarlo.

Come visibile dall’immagine la DreamSourceLab ha realizzato diverse versioni dello stesso prodotto (upgrade hardware) nonché alcuni prodotti differenti tra i quali tre serie di analizzatori logici e un’altrettanta serie di oscilloscopi USB.

In questa sede ci si concentrerà sull’analizzatore logico DSLogic Plus USB venduto al prezzo, IVA esclusa, di 149$ (circa 125€ IVA Esclusa). Trattasi di un analizzatore logico caratterizzato da:

- 16 ingressi digitali;

- Memoria RAM 256Mb 166MHz/CL3 o 133MHz/CL2;

- Sample Rate fino a 400MHz al più su 4 canali e in modalità buffer;

- Tempo minimo acquisizione impulsiva 5ns;

Si rimanda alla lettura del datasheet riportato in basso per l’elenco di tutte le specifiche di questo particolare prodotto che è la base della sua categoria.

DSLogic_Plus_USB_Datasheet

Esternamente si presenta in un piccolo contenitore di dimensioni “79mm x 74mm” in alluminio nero anodizzato e finemente spazzolato. La confezione è completa di test lead, test hook e cavo USB.

Su un lato del contenitore è presente il connettore USB tipo C, dal lato opposto i connettori per i test lead e in alto un led bicolore; rosso quando non riconosciuto/non collegato al programma DSView, verde in caso contrario.

I connettori lato analizzatore logico consistono di un classico header PCB con passo 0.05 pollici (1,27mm), la metà dello standard montato pressoché in ogni dispositivo e corrispondente a 0.1 pollici (2,74 mm).

La parte bassa del connettore, tutti i pin dalla parte opposta rispetto alla posizione della numerazione, identifica i collegamenti a massa; questo vuol dire che ogni singolo canale, leggasi ingresso e di riflesso ogni test lead, ha il corrispondente pin di massa.

Gli slot visibili (le fessure) subito in basso permettono un solido collegamento meccanico ottenuto con il dente del PCB dei connettori di ogni test lead. Un singolo test lead porta con se un gruppo di 4 ingressi quindi 4 cavetti coassiali con annessa filo di massa per ognuno di essi. I cavi di ogni test lead hanno una lunghezza di 25cm e lato connettore presenta un piccolo PCB avvolto da una guaina di gomma (sicuramente di tipo termorestringente) e sul quale trovano posto alcuni componenti e le pad per le saldature dei cavi come riportato nella varie fotografie visibili in basso.

Quando si misura un segnale, qualunque esso sia, una elevata velocità di campionamento non è sufficiente, occorre assicurarsi che il segnale, soprattutto via via che si va su in frequenza, possa essere rilevato e misurato nelle sue caratteristiche con il più basso valore di distorsioni possibile e questo nell’intero percorso di acquisizione. Per tale motivo una certa cura dovrà essere posta nei cavi/sonde di collegamento tra il punto del circuito che si vuole misurare e il sistema che dovrà acquisire quel segnale.

Molti analizzatori logici – tipicamente quelli più economici – presentano semplicemente dei “cavi volanti” che a tutti gli effetti si comportano come degli induttori e quindi all’atto pratico è come se si collegasse un’induttanza di un dato valore alla grandezza da misurare nel sistema sotto test inducendo così strani comportamenti nel segnale che si sta misurando alterandone, di riflesso, in maniera più o meno sensibile le caratteristiche e quindi le conclusioni che si possono trarre da una siffatta misura. Se si vogliono evitare distorsioni e attenuazioni del segnale, riflessioni indesiderate ecc non si potrà che avere una certa cura nei collegamenti e nei cavi che portano il segnale dal sistema sotto misura al sistema di misura.

Nel caso dell’analizzatore logico della DreamSourceLab viene utilizzato per ogni segnale un sottile cavo coassiale – segnale+massa – che si divide solo verso la fine, negli ultimi 3cm circa, del cavo stesso dove si ha la connessione agli “uncini”. Questo accorgimento permette una importante riduzione dell’induttanza nonché, avendo gli ultimi centimetri scoperti, il loop che si viene a creare è molto ridotto rispetto ad altre soluzioni a “cavi volanti”, e tale riduzione comporta di riflesso una riduzione dello “effeto antenna” e con esso una minore distorsione del segnale (naturalmente non esistono soluzioni ideali!). Una soluzione di questo tipo comporta un carico dei cavi più uniforme al variare della frequenza (almeno entro certi limiti, soprattutto superiori) che vedranno per la maggior parte l’impedenza caratteristica del cavo quindi con una risposta piatta del cavo al variare della frequenza almeno nei limiti indicati dal costruttore (salvo verifiche!).

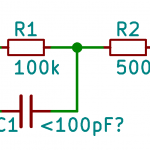

NOTA: la quarta e quinta fotografia mostrano i compoennti presenti sul PCB dei test lead. Per ovvi motivi pratici, legati al fatto che il taglio della guaina che avvolge il PCB è “distruttivo”, sono state prese dal sito del progetto Sigrok. La sesta fotografia, anche questa presa da Sigrok, riporta il circuito equivalente di ogni singolo cavetto dei quattro costituenti un singolo test lead.

L’hardware (teardown)

Dopo una breve disamina esterna passiamo a vedere la parte interna. L’hardware è accessibile attraverso quattro viti di colore nero, riportate sul lato opposto dove è presente il LED bicolore, che permettono di rimuovere il pannello inferiore del contenitore (immagine a lato, click per ingrandirla).

Dopo una breve disamina esterna passiamo a vedere la parte interna. L’hardware è accessibile attraverso quattro viti di colore nero, riportate sul lato opposto dove è presente il LED bicolore, che permettono di rimuovere il pannello inferiore del contenitore (immagine a lato, click per ingrandirla).

Per la rimozione del PCB è necessario rimuovere le ulteriori 4 viti visibili quindi fare delicatamente leva con un piccolo cacciavite dalla parte del contenitore USB senza forzare e contemporaneamente spingere il PCB verso il connettore header a 32 pin. Eseguita l’operazione è possibile dividere il PCB dal contenitore.

Nel seguito si riportano i datasheet dei semiconduttori visibili.

Il chip CY7C68013A in package QFN (Quad-Flat No-lead) a 56 pin (14 per lato) è della società americana di progettazione e produzione di semiconduttori Cypress Semiconductor Corporation (oggi una sussidiaria della teutonica Infineon Technologies). Un bus adapter high speed USB peripheral controller che riceve i dati dalla FPGA e li impacchetta in maniera tale da adattarsi alla trasmissione via USB, viceversa per i dati ricevuti dalla porta USB. Presenta al suo interno un microcontrollore con core 8051 tramite il quale viene effettuata, tra le altre funzioni, la supervisione della comunicazione tra analizzatore logico e PC. In basso viene riportato il datasheet del componente.

Il chip CY7C68013A in package QFN (Quad-Flat No-lead) a 56 pin (14 per lato) è della società americana di progettazione e produzione di semiconduttori Cypress Semiconductor Corporation (oggi una sussidiaria della teutonica Infineon Technologies). Un bus adapter high speed USB peripheral controller che riceve i dati dalla FPGA e li impacchetta in maniera tale da adattarsi alla trasmissione via USB, viceversa per i dati ricevuti dalla porta USB. Presenta al suo interno un microcontrollore con core 8051 tramite il quale viene effettuata, tra le altre funzioni, la supervisione della comunicazione tra analizzatore logico e PC. In basso viene riportato il datasheet del componente.

DSLogic_Plus_USB_CY7C68013A

La presenza di un core 8051 all’interno del chip della Cypress fa presagire un firmware immagazzinato da qualche parte affinché possa essere caricato dall’8051 all’atto dell’accensione. Il suddetto firmware è presente all’interno di una 128-Kbit serial I2C bus EEPROM (Electrically Erasable Programmable Memory) M24128-BR in package SO8N (Small Outline 8-lead) della italo-francese STMicroelectronics per la produzione di componenti elettronici a semiconduttore il cui datasheet viene riportato in basso. Osservare come i pin 5 e 6, rispettivamente SDA (Serial DAta) e SCL (Serial CLock) del bus IIC, vadano a collegarsi rispettivamente ai piedini 16 (SDA) e 15 (SCL) dell’USB controller della Cypress.

La presenza di un core 8051 all’interno del chip della Cypress fa presagire un firmware immagazzinato da qualche parte affinché possa essere caricato dall’8051 all’atto dell’accensione. Il suddetto firmware è presente all’interno di una 128-Kbit serial I2C bus EEPROM (Electrically Erasable Programmable Memory) M24128-BR in package SO8N (Small Outline 8-lead) della italo-francese STMicroelectronics per la produzione di componenti elettronici a semiconduttore il cui datasheet viene riportato in basso. Osservare come i pin 5 e 6, rispettivamente SDA (Serial DAta) e SCL (Serial CLock) del bus IIC, vadano a collegarsi rispettivamente ai piedini 16 (SDA) e 15 (SCL) dell’USB controller della Cypress.

DSLogic_Plus_USB_M24128

Il cuore dell’analizzatore è l’FPGA (Field Programmable Gate Array) della americana Xilinx uno dei principali produttori di dispositivi logici programmabili (PLD, Programmable Logic Device). Trattasi di una XC6SLX9 in package TQFP (Thin Quad Flat Pack) da 144 pin caratterizzata da 9.152 celle logiche. È l’upgrade hardware promesso qualora i pledge su Kickstarter avessero raggiunto i $30.000 come poi è accaduto. Tra le altre cose integra un Memory Controller Blocks per RAM DDR, DDR2, DDR3 e LPDDR. Riceve in ingresso i campioni dei dati da analizzare, li impacchetta per trasferirli al controller USB Cypress quindi attraverso il connettore USB vengono inviati al PC.

Il cuore dell’analizzatore è l’FPGA (Field Programmable Gate Array) della americana Xilinx uno dei principali produttori di dispositivi logici programmabili (PLD, Programmable Logic Device). Trattasi di una XC6SLX9 in package TQFP (Thin Quad Flat Pack) da 144 pin caratterizzata da 9.152 celle logiche. È l’upgrade hardware promesso qualora i pledge su Kickstarter avessero raggiunto i $30.000 come poi è accaduto. Tra le altre cose integra un Memory Controller Blocks per RAM DDR, DDR2, DDR3 e LPDDR. Riceve in ingresso i campioni dei dati da analizzare, li impacchetta per trasferirli al controller USB Cypress quindi attraverso il connettore USB vengono inviati al PC.

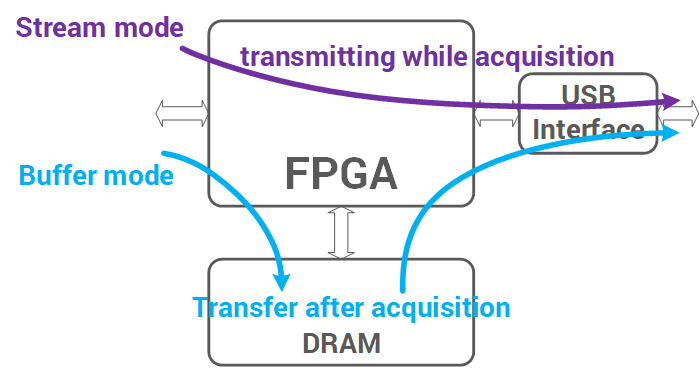

DSLogic_Plus_USB_Spartan6_Family_Overview

La velocità di trasferimento dei dati per questo modello di analizzatore logico è legata al tipo di connessione USB che è una 2.0 portando così il limite superiore (teorico) a non oltre i 200 Mb/s. Comunque sufficientemente veloce da poter immaginare un trasferimento in tempo reale al PC nella modalità streaming mode (percorso in viola nella fotografia in basso) qualora gli stessi segnali non presentino una velocità superiore a quella massima ammissibile dalla velocità teorica di trasferimento. In questa modalità non vi è alcun limite sull’ammontare dei dati che possono essere trasferiti in tempo reale al computer. Il limite superiore è indotto dalle risorse del computer stesso il quale dovrà elaborare, memorizzare e visualizzare i dati che gli arrivano di continuo dall’analizzatore il quale trasmette via via che acquisisce.

La modalità streaming mode cade in difetto nel momento in cui il segnale o i segnali da analizzare sono sempre più veloci e in numero crescente. In questo scenario la velocità di trasferimento della USB 2.0 non permette più un trasferimento in tempo reale dei dati se il loro ammontare raggiunge e va oltre il limite superiore (in realtà teorico) dei 200 Mb/s. In questi casi è da preferire la modalità buffer mode (percorso azzurro nell’immagine in alto) che comunque risulta essere limitata in velocità in funzione del numero di acquisizione contemporanee (si legga il datasheet riportato in alto).

Le acquisizioni nella modalità buffer mode nella DRAM dell’analizzatore logico. Inizialmente la capacità era di 64Mb ma raggiunto in Kickstarter il pledge dei 50.000$ ne è stato fatto, come da progetto, un upgrade con una memoria da 256Mb. Di preciso una W9825G6KH-6 (immagine a lato, un click per ingrandirla. In basso ne viene riportato il datasheet) in package TSOP (Thin Small Outline Package) Tipo 2 da 54 pin realizzata dalla taiwanese Winbond produttrice di semiconduttori e diversi tipi di circuiti integrati come RAM dinamiche e statiche, flash, microcontrollori e circuiti integrati in generale. È evidente come la RAM entri in scena quando l’analizzatore opera modalità buffer; i campioni dei segnali ad alta velocità (al più 400MHz su al più 4 ingressi, un valore di tutto rispetto!) vengono immagazzinati nella RAM. Sarà cura della FPGA operare il trasferimento dei dati dalla memoria RAM alla porta USB (ovvero al computer) coadiuvata dal chip della Cypress.

Le acquisizioni nella modalità buffer mode nella DRAM dell’analizzatore logico. Inizialmente la capacità era di 64Mb ma raggiunto in Kickstarter il pledge dei 50.000$ ne è stato fatto, come da progetto, un upgrade con una memoria da 256Mb. Di preciso una W9825G6KH-6 (immagine a lato, un click per ingrandirla. In basso ne viene riportato il datasheet) in package TSOP (Thin Small Outline Package) Tipo 2 da 54 pin realizzata dalla taiwanese Winbond produttrice di semiconduttori e diversi tipi di circuiti integrati come RAM dinamiche e statiche, flash, microcontrollori e circuiti integrati in generale. È evidente come la RAM entri in scena quando l’analizzatore opera modalità buffer; i campioni dei segnali ad alta velocità (al più 400MHz su al più 4 ingressi, un valore di tutto rispetto!) vengono immagazzinati nella RAM. Sarà cura della FPGA operare il trasferimento dei dati dalla memoria RAM alla porta USB (ovvero al computer) coadiuvata dal chip della Cypress.

DSLogic_Plus_USB_W9825G6KH

Fanno da contorno ulteriori semiconduttori tra i quali, nell’immagine a lato, ne vengono posti in evidenza altri due. Al di là del fusibile, del diodo, del condensatore C50 e delle due induttanze siglate L1 e L2 che fanno presagire la presenza di due tensioni differenti che sicuramente andranno ad alimentare il core della FPGA, sulla sinistra troviamo il primo semiconduttore il chip recante la sigla BQE391AKEL. Trattasi di un 10 pin leadless TPS62400 (datasheet riportato in basso), un Dual, Adjustable, 400mA e 600mA, 2.25MHz Step-Down Converter della statunitense Texas Instruments disponibile in package VSON (Very Small Outline No-lead) della dimensione di 3mm*3mm. Sulla destra è visibile un piccolo chip 3+3 pin la cui funzione è analoga a quella descritta nel seguito per la sezione di ingresso per analoghi chip.

Fanno da contorno ulteriori semiconduttori tra i quali, nell’immagine a lato, ne vengono posti in evidenza altri due. Al di là del fusibile, del diodo, del condensatore C50 e delle due induttanze siglate L1 e L2 che fanno presagire la presenza di due tensioni differenti che sicuramente andranno ad alimentare il core della FPGA, sulla sinistra troviamo il primo semiconduttore il chip recante la sigla BQE391AKEL. Trattasi di un 10 pin leadless TPS62400 (datasheet riportato in basso), un Dual, Adjustable, 400mA e 600mA, 2.25MHz Step-Down Converter della statunitense Texas Instruments disponibile in package VSON (Very Small Outline No-lead) della dimensione di 3mm*3mm. Sulla destra è visibile un piccolo chip 3+3 pin la cui funzione è analoga a quella descritta nel seguito per la sezione di ingresso per analoghi chip.

DSLogic_Plus_USB_Spartan6_Family_Overview_TI_TPS62400

La sezione AFE (Analog Front-End) è caratterizzata – immagine in basso – da una serie di protezioni per ogni singolo ingresso afferente alla FPGA. Il circuito di ingresso vede resistenze di pull-down da R51 a R66 visibili in basso nell’immagine a fianco del valore di 7,6kΩ. Queste resistenze, per ogni singolo ingresso, permettono di mantenerne basso il livello logico quando nessun segnale è applicato impedendo eventuali ricezioni di spike, problemi di crosstalk e tutto ciò che comporterebbe la “funzione di antenna” dei cavi del test lead non collegati. Questo significa che una lettura da quegli ingressi determinerà sempre un valore logico basso. Allo stesso capo della resistenza sono collegati gli integrati indicati con U6, U7, U8, U9 e U10 in package SOT-326 (Small Outline Transistor). Probabilmente trattasi di 4-Channel Low Capacitance ESD Protection Arrays della statunitense ON Semiconductor siglati CM1213A−04S7 (datasheet in basso). Sono dispositivi di protezione contro scariche elettrostatiche caratterizzati da 8 diodi di clamping – 1 coppia per ogni canale – e un diodo zener.

La sezione AFE (Analog Front-End) è caratterizzata – immagine in basso – da una serie di protezioni per ogni singolo ingresso afferente alla FPGA. Il circuito di ingresso vede resistenze di pull-down da R51 a R66 visibili in basso nell’immagine a fianco del valore di 7,6kΩ. Queste resistenze, per ogni singolo ingresso, permettono di mantenerne basso il livello logico quando nessun segnale è applicato impedendo eventuali ricezioni di spike, problemi di crosstalk e tutto ciò che comporterebbe la “funzione di antenna” dei cavi del test lead non collegati. Questo significa che una lettura da quegli ingressi determinerà sempre un valore logico basso. Allo stesso capo della resistenza sono collegati gli integrati indicati con U6, U7, U8, U9 e U10 in package SOT-326 (Small Outline Transistor). Probabilmente trattasi di 4-Channel Low Capacitance ESD Protection Arrays della statunitense ON Semiconductor siglati CM1213A−04S7 (datasheet in basso). Sono dispositivi di protezione contro scariche elettrostatiche caratterizzati da 8 diodi di clamping – 1 coppia per ogni canale – e un diodo zener.

DSLogic_Plus_USB_CM1213A

Questa rete, collegata ad ogni ingresso della FPGA, permette di proteggerla da eventuali scariche elettrostatiche così come da inaspettati/imprevedibili spike e più in generale dai segnali spuri di tensioni presenti sul sistema che si sta misurando. A questa misura di protezione si aggiungono anche i diodi di protezione (clamping) presenti all’interno della FPGA in ogni ingresso.

La corrente in ingresso o in uscita da ogni pin della FPGA – in funzione del livello di tensione positivo o negativo – viene limitata attraverso le resistenze da 30Ω a gruppi di 4 siglate R23, R25, R27 e R29 così come R31, R33, R35 e R37 e così via per gli altri gruppi.

Infine, tra i vari componenti passivi, sul lato “bottom” del PCB trova posto il quarzo da 24MHz.

Il software

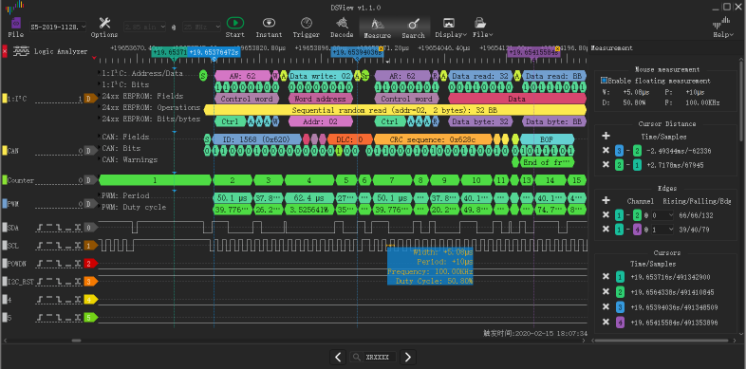

Il software di visualizzazione fornito dalla DreamSourceLab è DSView una “rivisitazione” di PulseView del progetto Sigrok richiamato nel paragrafo precedente.

Ho già riportato la dinamica per la compilazione da sorgenti nell’articolo DSView, compilare il programma da sorgenti, pertanto in questo contesto riporterò semplici misure a diverse frequenze.

Nel fare le misure occorre ricordare i limiti in funzione della modalità di funzionamento impostata, se in buffer mode, per il modello DSLogic Plus:

– 4 canali 400MHz;

– 8 canali 200MHz;

– 16 canali 100MHz.

Qualora si volesse operare in streaming mode i limiti di validità, relativi al modello DSLogic Plus, sono:

– 3 canali 100MHz;

– 6 canali 50MHz;

– 12 canali 25MHz;

– 16 canali 20MHz.

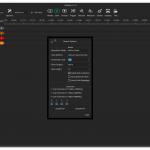

La scelta, in funzione del segnale da misurare, una volta collegato l’analizzatore logico alla porta USB e lanciato DSView, la si può fare direttamente dall’icona in alto a sinistra Options e nella relativa finestra di pop-up come riportato in basso per la modalità buffer e streaming e dalla quale è possibile impostare altri parametri come l’utilizzo di un clock esterno, il livello di soglia del trigger e altro ancora.

Per le modalità d’uso del software (in realtà abbastanza intuitive) si rimanda al manuale utente riportato in basso in formato pdf.

DSLogic_Plus_USB_DSView_User_Guide

Prime generiche misure

Il supporto a una pletora di protocolli potrebbe indurre nell’imbarazzo della scelta di una prova in luogo di un’altra, e.g. mettere su un sistema prototipale con integrati che utilizzano i protocolli più comuni come I2C, SPI, 1-Wire PWM e UART. Non sono un problema poiché il supporto rimane comunque in software attraverso le librerie Sigrok. Ma non sarà così, in questa prima prova voglio solo verificare la bontà delle misure dell’ordine dei MHz confrontandole con i risultati visibili sullo schermo di un oscilloscopio.

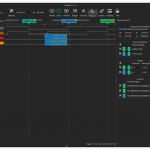

Prima prova: due ingressi 4MHz e 8MHz

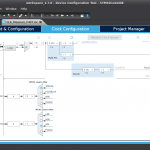

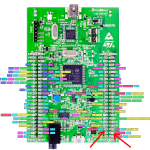

Nella prima prova effettuerò la misura di due frequenze 4MHz e 8MHz e per ottenerle mi avvalgo di una Discovery Kit Board con a bordo un ARM Cortex-M4 STM32F407VG. In GNU/Linux utilizzando il software STM32CubeIDE della STMicroelectronics abilito le uscite MCO (Microcontroller Controller Output) e di preciso le MCO1 e MCO2 le quali vengono mappate rispettivamente sui pin PA8 e PC9 dell’ARM Cortex-M4; queste uscite vengono utilizzate generalmente per pilotare in sincrono altri microcontrollori, in questo specifico caso ipotizzo la presenza su PC9 di un micro a 4MHz e la presenza su PA8 di un micro a 8MHz.

Per questa prova utilizzo il clock HSI (High Speed Internal) dell’ARM Cortex-M4, in sostanza una coppia R-C integrata nel chip che oscilla a 16MHz. Naturalmente rispetto ad un oscillatore quarzato risulterà sicuramente meno stabile e più influenzato dalla variazione della temperatura, ma per la prova in questione non è di interesse. Le uscite PA8 e PC9 sulla scheda in uso sono fisicamente presenti nei punti indicati dalle frecce nell’immagine in basso. La misura verrà effettuata dapprima con l’oscilloscopio (cablaggio e screenshot nelle figure in basso) quindi verrà utilizzato l’analizatore logico in modalità buffer mode a 400MHz campionando 100ms di tempo. L’ordine delle immagini indica anche l’ordine dei passaggi seguiti.

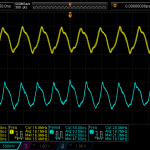

Seconda prova; si sale in frequenza

Si potrebbe pensare di salire in frequenza, idealmente fino a 168MHz. In realtà la lunghezza delle connessioni (piste del PCB) sulla scheda unitamente alla presenza dei cavi/sonde porteranno inevitabilmente alla degradazione del segnale già a frequenze non troppo elevate.

La prova successiva vede sempre l’utilizzo dell’ARM Cortex-M4 sulla stessa scheda ma questa volta impostando le uscite MCO1 e MCO2 rispettivamente a 16MHz e 20MHz. L’importante attenuazione del segnale nonché la sua distorsione impongono di lavorare un po’ sul trigger dell’analizzatore logico, ma anche con queste forme d’onda decisamente degradate non si ha alcun problema nella loro analisi/rilevazione. La sequenza delle operazioni è esattamente la stessa del passo precedente. Modalità utilizzata buffer mode a 100MHz e 100ms di campioni. Va da se che la degradazione del segnale altera il duty-cycle dell’onda (ammesso che in queste condizioni si possa ancora parlare di duty-cycle!)

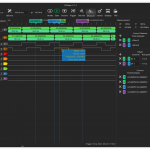

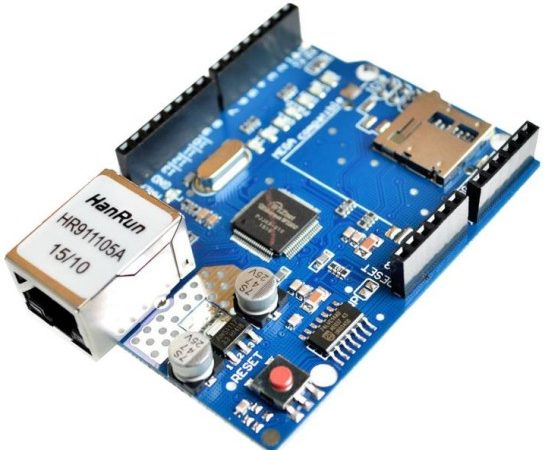

Terza prova; 32MHz

Voglio salire un po’ in frequenza e per evitare di degradare ulteriormente il segnale utilizzo una scheda più piccola (quindi minor lunghezza delle piste del PCB) e di preciso una Nucleo-64 STM32F103RB un ARM Cortex-M3. Al solito attraverso il software STM32CubeIDE configuro il Clock Configuration per l’unica uscita MCO che presenta questo ARM per fornire in uscita 32MHz ed eseguo la stessa procedura vista per i due passaggi precedenti. Il pin PA8 è mappato fisicamente sul connettore Arduino (l’interno a destra) oppure sul connettore CN10 posta a destra della scheda (immagine al lato indicato con una freccia). Il segnale risulta sempre degradato e in forma così come in ampiezza; l’analizzatore logico è in buffer mode a 400MHz con un campione temporale di 50ms.

Voglio salire un po’ in frequenza e per evitare di degradare ulteriormente il segnale utilizzo una scheda più piccola (quindi minor lunghezza delle piste del PCB) e di preciso una Nucleo-64 STM32F103RB un ARM Cortex-M3. Al solito attraverso il software STM32CubeIDE configuro il Clock Configuration per l’unica uscita MCO che presenta questo ARM per fornire in uscita 32MHz ed eseguo la stessa procedura vista per i due passaggi precedenti. Il pin PA8 è mappato fisicamente sul connettore Arduino (l’interno a destra) oppure sul connettore CN10 posta a destra della scheda (immagine al lato indicato con una freccia). Il segnale risulta sempre degradato e in forma così come in ampiezza; l’analizzatore logico è in buffer mode a 400MHz con un campione temporale di 50ms.

Non avendo, al momento di queste prove, la possibilità di generare frequenze superiori (ho un generatore di segnali SIGLENT SDG1025 che si ferma a 25MHz) per la prima analisi di questo analizzatore logico mi fermo qui. Quando avrò la possibilità di un PLL che possa salire in frequenza almeno sui 200MHz proverò ad eseguire ulteriori prove. Se nel frattempo qualcuno avesse eseguito questo tipo di prove può sempre scriverlo nei commenti in basso affinché sia possibile visionarle.